7 存储器

一个存储矩阵有64行、64列,则存储阵列的存储容量为()个存储单元。

2048

4K

1024

4M

利用ROM实现四位二进制码到四位格雷码的转换,则该ROM的数据线有4根,地址线有()根。

4

8

2

10

用ROM实现两个3位二进制数相乘的乘法器时,所需的容量至少为()。

\( 2^3\times 3 \) 位

\( 2^6 \times 3 \) 位

\( 2^6 \times 6 \) 位

\( 2^3 \times 6 \) 位

利用ROM实现两个4位二进制数相乘的功能,则该ROM的地址线有()根,数据线有()根。

16,8

8,8

10,10

4,8

一个1024*8位的ROM,地址线为()根。

10

12

7

8

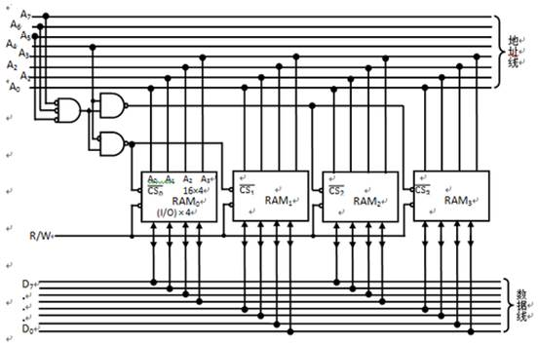

如下图所示的RAM芯片组成的存储器,存储器的总容量是()。

64*8

32*8

64*4

32*4

将256*1位ROM扩展为1024*8位ROM,共需()片256*1位ROM.

32

10

64

16

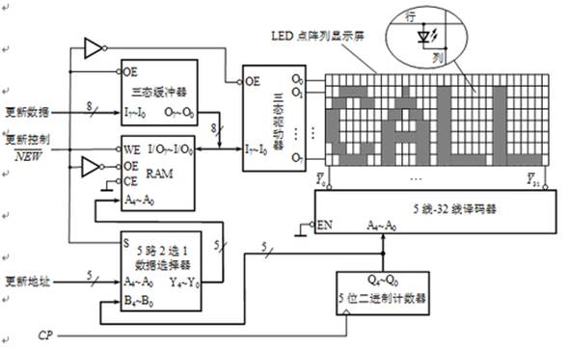

在下图所示的LED点阵列字符动态显示电路中,若人的视觉暂留时间为0.05s,在满足LED阵列图像稳定不闪烁的情况下,CP脉冲的最低工作频率为()。

500Hz

1kHz

640Hz

100Hz

一个16K*4的存储系统的起始地址为全0,其最高地址的十六进制地址码为()。

3FFF H

FFFF H

8FFF H

3FFFF H

用ROM可以实现各种组合逻辑函数。在设计实现时,只需列出真值表,逻辑函数的输入作为存储内容,输出作为地址,将内容按地址写入ROM即可。判断对错()

Answer

B \( 2^6\times 2^6 = 2^12 = 4\times 2^10 = 4K \)

A 地址线是输入信号,为4根,对应4个二进制码

C (111B)*(111B)=49 D,所以乘积结果最大为49,占6bit,所以数据线是6根; 输入为2个3位二进制数,所以地址线是6根。答案就是C。

B 四位二进制最大是15,两个相乘最大是225,需要占8bit,所以数据线是8根;输入2个四位二进制数,是8根线。

A \( 1024 = 2^10 \),所以地址线是10.

B 数据线是8根,地址线是5根,答案是32*8。容量是4*(16*4)=256, 推测地址线是:256/8=32。图中8根,组合之后,实际起作用的是5组。

A 先位扩展需要8片一组,变成8位宽;然后字扩展,需要4组。所以共需要4*8片。

C 5-32译码器的每一位的频率需要至少为1/0.05s=20Hz,它还需要32位轮流一次,所以整体需要20*32=640Hz。

A 16K=2^14,需要14根地址线,最大为3FFF h= 11 1111 1111 1111 h。

False 错,反了。输入接地址线,输出作为存储内容。