5 锁存器与触发器

以下关于锁存器和触发器描述正确的是()

锁存器是脉冲边沿敏感器件,触发器是脉冲电平敏感器件

锁存器是脉冲电平敏感器件,触发器是脉冲边沿敏感器件

锁存器和触发器都是脉冲边沿敏感器件

锁存器和触发器都是脉冲电平敏感器件

当输入端S和R为(),由或非门构成的基本SR锁存器可能会在它们撤销时出现不稳定状态。

S=0,R=1

S=1,R=1

S=0,R=0

S=1,R=0

对于门控D锁存器来说,在()条件下,输出端Q总是等于输入的数据D。

使能脉冲之后的瞬间

使能脉冲之前

任何时候

使能脉冲期间

触发器有()个稳定状态,它可以存储1位二进制码,存储8位二进制信息需要()个触发器。

1,2

2,2

2,4

2,8

触发器被清零(复位)后,\(Q\)和\(\overline{Q}\)端的状态分别为 ()

1,0

0,1

1,1

0,0

触发器的输出逻辑电平从1到0或从0到1的转换称为()

置位

保持

清零

翻转

触发器CP输入端的三角形符号指的是()

电平触发

低电平有效输入

高电平有效输入

边沿触发

触发器CP输入端的 ∘ 符号指的是 ()

电平触发

上升沿触发

下降沿触发

边沿触发

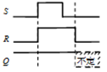

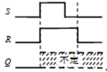

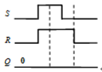

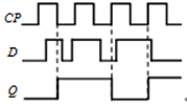

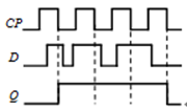

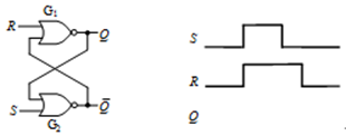

假定锁存器的初始状态为0。对于下图所示的电路和输入波形,输出端Q的波形图为()

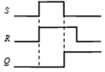

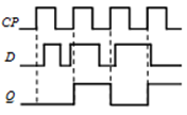

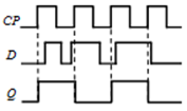

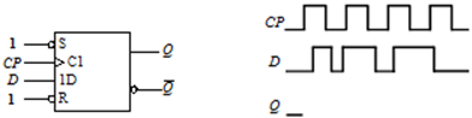

在下图中,假设触发器的初态均为0,则Q的波形图为()。

Answer

B 选项B是正确的。锁存器是电平敏感的,触发器是边沿敏感的。

B 或门为1有效,S、R同时有效时,输出Q和Q非均为1,同时撤离时,由于撤离不可能完全同步,则会出现不稳定状态。

D 门控D锁存器为电平敏感的,即使能端在有效时,总有Q=D。

D 触发器有0、1两个稳定状态。8bit需要8个触发器。

B 清零后Q为0,Q非为1。

D 状态变为相反状态,称之为翻转。

D 三角形代表边沿触发,没有三角形代表电平触发。

C 无圈代表上升沿触发,有圈代表下降沿触发。

C 选项C是正确的,初始状态为0,当S=R=0时,先保持为0;当S=R=1时,置为0;当S=0,R=1时,置为0;当S=R=0时,继续保持为0。因此Q一直为0。

C 触发器的异步置位端S和R一直是无效的,不用管它们。查看每个CP的上升沿,以及它到来前的D的状态,使得Q=D。