4 组合逻辑电路

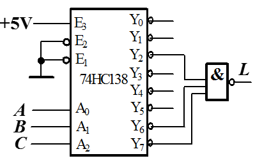

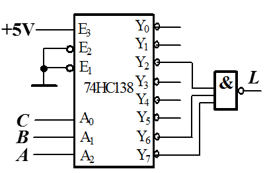

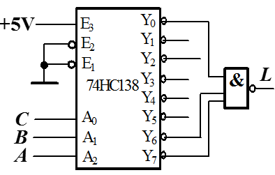

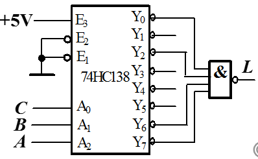

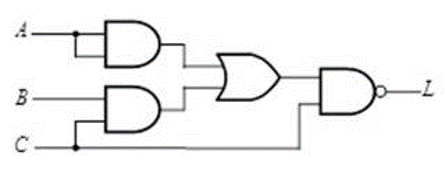

电路如图所示,输出端L的表达式为()

\( L=ABC \)

\( L=\overline{ABC} \)

\( L=\overline{A}\cdot \overline{B}+\overline{C} \)

\( L=\overline{AB}C \)

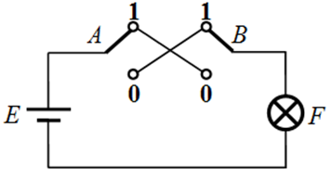

由开关组成的逻辑电路如图所示,设开关A、B分别有如图所示为“0”和“1”两个状态,则电灯F亮的逻辑式为()。

\( F=\overline{A}B+AB \)

\( F=A\overline{B}+AB \)

\( F=\overline{A}\overline{B}+AB \)

\( F=\overline{A}B+A\overline{B} \)

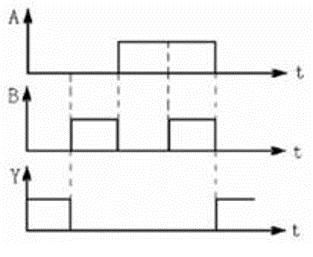

下图中,A、B为某逻辑电路的输入波形,Y为输出波形若采用一个单个的门电路实现,则该逻辑电路为()

或非门

与门

与非门

同或门

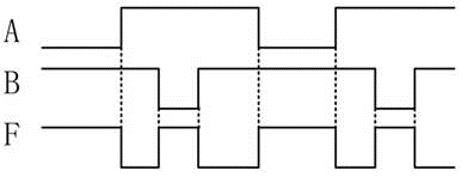

已知二变量输入逻辑门的输入A、B和输出F的波形如图所示,若采用单一门电路,则该逻辑电路为()。

同或门

异或门

与非门

无法判断

如图所示电路中,Y(A, B, C, D)的最小项表达式是()

\( Y=\sum m\left( 1,2,3,4 \right) \)

\( Y=\sum m\left( 3,5,6,7 \right) \)

\( Y=\sum m\left( 0,1,2,3,4 \right) \)

\( Y=\sum m\left( 5,6,7 \right) \)

组合逻辑电路中的竞争冒险是由()引起的。

最小项

最大项

门电路的组合

门电路的延时

下列表达式中不存在竞争冒险的有().

\( Y=\left( A+\overline{B} \right) \overline{A\overline{D}} \)

\( Y=AB\overline{C}+AB \)

\( Y=AB+\overline{B}C \)

\( Y=\overline{B}+\overline{A}B \)

函数 \( F = \overline{A}C + AB + \overline{B}\overline{C} \),当变量的取值为()。将不出现冒险现象。

A=0,B=0

A=1,C=0

B=C=1

B=C=0

关于组合逻辑电路的描述错误的是()

不考虑门电路的延时,组合逻辑电路的输出可以被认为是随输入信号瞬变的;

组合逻辑电路不具有记忆功能;

组合逻辑电路中不存在输出到输入的反馈通路;

组合逻辑电路中一定存在竞争与冒险,必须消除。

关于编码器的说法正确的是()

编码器是将 \( 2^N \) 个状态编成 \(N\) 个码

编码器是最多将 \( 2^N \) 个状态编成 \(N\) 个码

编码器是将 \( N \) 个状态编成 \( 2^N \) 个编码

编码器是将 \( N \) 个状态最多编成 \( 2^N \) 个编码

一个8421BCD码译码器的数据输入线与译码输出线的组合是()。

4:6

1:10

4:10

2:4

设计一个对1000个符号进行二进制编码,则至少要()位二进制数码。

10

11

1000

3

当七段显示译码器的七个输出端状态为abcdefg =0011111时(高电平有效),译码器输入状态(8421BCD码)应为()。

0100

0101

0011

0110

普通编码器的2个或2个以上的输入同时为有效信号时,输出将出现错误编码。对吗?

当2个或2个以上的输入同时为有效信号时,优先编码器将只对优先级别高的输入进行编码。对吗?

采用译码器可以实现任意逻辑函数,如实现 \( L = AB + B\overline{C} \),则以下电路连接正确的是 () 注意A2为高位,A0为低位。

下列哪个是37的8421 BCD码()

0010 0101

0011 0111

0111 0011

0101 0010

一个8位无符号二进制数原码需要显示时,需要转换为几组4位的8421 BCD码()

2组,分别显示十位、个位

3组,分别显示百位、十位、个位

4组,分别显示千位、百位、十位、个位

5组,分别显示万位、千位、百位、十位、个位

一个十六路数据选择器,其地址输入(选择控制端输入)端有()个。

4

16

2

8

用四选一数据选择器实现函数 \( Y = A_1A_0 + \overline{A_1}A_0 \),应使 ()。

D0=D2=0, D1=D3=1

D0=D2=1, D1=D3=0

D0=D1=1, D2=D3=0

D0=D1=0, D2=D3=1

一个十进制——8421 BCD码的编码器的数据输入线与输出线的组合是()。

1:10

4:10

10:4

4:6

设计一个对100个符号进行进制编码,则至少要()位二进制数码。

100

7

8

6

设计一个裁判表决电路。裁判组由三个人组成:主裁判A、副裁判B和C。在判定一次比赛的结果时必须按照如下原则:只有当两个或两个以上裁判支持,并且其中有一一个为主裁判时,比赛结果的裁决才有效。令A、B、C为1表示支持,为0表示反对。裁决Y为1表示有效,为0表示无效。下列表达式中能够实现该电路功能的是()。

Y=A+ BC

Y=ABC

Y=A+B+C

Y=AB+AC

设计一个4输入的二进制码奇校验电路,需要()个异或门。

2

4

3

5

多路数据分配器可以直接由来实现。

译码器

编码器

多路数据选择器

多位加法器

实现两个一位二进制数和来自低位的进位相加的电路叫全加器。对吗?

串行进位加法器的缺点是运算速度慢,优点是电路结构简单。超前进位加法器的优点是运算速度快,缺点是电路结构复杂。对吗?

Answer

C 根据逻辑电路图可以写出表达式,反演律和吸收律,化简为C。

D 图中A和B路为异或关系,相异时,电路接通。所以答案为异或的表达式,即D。

A 根据图中输出Y为1的地方,写出Y的表达式为 \( Y=\overline{A}\overline{B}=\overline{A+B} \)。因此为或非门。

B 图中输出信号为1的地方,写出表达式\( Y = \overline{A}B + A\overline{B} \),因此为异或门。

D 根据图中写出表达式 \( Y=\overline{\overline{AB}\cdot \overline{AC}} \),去非号、去括号,写为与或形式,再写出最小项形式,结果为:\( Y=AB+AC=AB\overline{C}+ABC=\sum m\left( 5,6,7 \right) \)

D 答案为D,是由门电路的延时时间不同造成的。

B 选项B是正确的,不存在两个互补项。

D 选项D是正确的,B=C=0时,互补项不起作用,F=1

D 选项D中说法是错的,不一定存在竞争与冒险,只有存在互补项时才有竞争和冒险。

B 选项B正确,是最多将 \(2^N\) 个状态编成N个码,可以有多余的状态 例如8421-二进制编码就是10个状态编成4位码。

C 选项C是正确的,4位8421码输入,译码输出10个状态。

A 选项A正确,1000<1024=2^10,因此至少需要10位数据码。

D 选项D是6的8421码。

True 正确,普通编码器不允许两路同时有效。

True 正确

B 设A为最高位, \( L=AB+B\overline{C}=ABC+AB\overline{C}+\overline{A}B\overline{C}=\sum m\left( 2,6,7 \right) \) ,所以图B正确,注意A接高位A2,C接低位A0

B 选项B正确,十位、个位分别编码,各占四位。

B 选项B正确,3组,因为8位无符号数最大为255,因此需要百位、十位、个位分别编码,即3组8421BCD码。

A 16路输入,需要4个控制端输入。

A Y写成最小项的形式,Y=m1+m3。所以需要D1=1,D3=1。

C 该编码器的输入为10个状态,输出为4位的8421BCD码。

B 对100<2^7=128个符号编码,至少需要7位码。

D 根据描述可以写出真值表,然后再写出表达式,利用逻辑代数中的恒等式化简,可以写为: \( Y=AB+A\overline{B}C=AB+AC \)

C 4输入的奇偶校验电路需要3个异或门,即Y=((A⊕B)⊕C)⊕D.

A 数据分配器可以由译码器来实现,见ppt或书。

True 对

True 对