2.2 变量

net(线网类型)

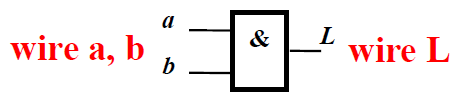

net型变量相当于硬件电路中的各种物理连接,其特点是输出的值紧跟输入值的变化而变化。常见的有wire、tri、wand、supply0等。举例:网络型变量L的值由与门的驱动信号

a和b所决定,即L=a&b。当a、b的值发生变化时,线网L的值会立即跟着变化。

wire是最常用的net型变量。// 格式 wire [n-1:0] var1, var2,...; // 举例 wire L; wire [7:0] databus;

驱动方式:

在结构描述中将其连接到一个门元件或模块的输出端;

用持续赋值语句

assign对其进行赋值。

variable(变量类型)

注意:教科书采用的Verilog-1995标准,

variable型变量称为register型(寄存器型);在Verilog-2001标准中将register一词改为了variable,以避免初学者将register和硬件中的寄存器概念混淆起来。variable类型变量必须放在过程语句(如initial、always)中,通过过程赋值语句赋值;在always、initial等过程块内被赋值的信号也必须定义成variable型。常见的

variable型变量有reg、integer、time、real、realtime等。这些类型是指抽象描述,不对应具体硬件,在综合器进行综合时根据具体情况来确定是映射成连线还是映射为触发器或寄存器。类型

说明

reg常用的寄存器型变量(可定义位宽)

integer32位有符号整数型变量

real64位有符号实数型变量

time64位无符号时间变量

reg是最常用的variable型变量。// 格式 reg [n-1:0] var1, var2,...; // 举例 reg clock; reg [3:0] counter;

标量与向量

宽度为1位的变量也称为标量,如果在变量声明中没有指定位宽,则默认为标量(1位)

线宽大于1位的变量也称为向量(vector),其宽度采用

[msb:lsb]定义。位选择和域选择:在表达式中可任意选中向量中的一位(位选择)或相邻几位(域选择)。举例如下:

reg [7:0] a, b; reg [3:0] c; reg d; d = a[7] & b[7]; //位选择 c = a[7:4] + b[3:0]; //域选择 c = a\[7:4\] + b\[3:0\]; //域选择