1.2 Verilog 模型描述方式

结构(Structural)描述方式

调用Verilog内置门元件(门级结构描述)

调用开关级元件(晶体管级结构描述)

用户自定义元件UDP(也在门级)

数据流(Data Flow)描述方式

主要使用持续赋值语句,多用于描述组合逻辑电路

行为(Behavioral)描述方式

对设计实体的数学模型的描述,其抽象程度远高于结构描述方式。

行为描述类似于高级编程语言,当描述一个设计实体的行为时,无需知道具体电路的结构,只需要描述清楚输入与输出信号的行为,而不需要花费更多的精力关注设计功能的门级实现

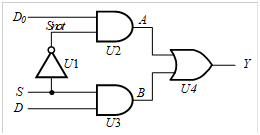

举例:用不同描述方式建立下图的Verilog模型

结构描述方式

module mux2to1(D0, D1, S, Y); input D0, D1, S; output Y; wire Snot, A, B; not U1(Snot, S); and U2(A, D0, Snot); and U3(B, D1, S); or U4(Y, A, B); endmodule

数据流描述方式:\( Y = \overline{S} \cdot D_0 + S \cdot D_1 \)

module mux2to1_dataflow(D0, D1, S, Y); input D0, D1, S; output Y; wire Y; assign Y = (~S & D0) | (S & D1); endmodule

行为描述方式

module mux2to1_bh(D0, D1, S, Y); input D0, D1, S; output Y; reg Y; always @(S or D0 or D1) if (S == 1) Y = D1; // if (S) Y = D1; else Y = D0; endmodule