5 锁存器和触发器

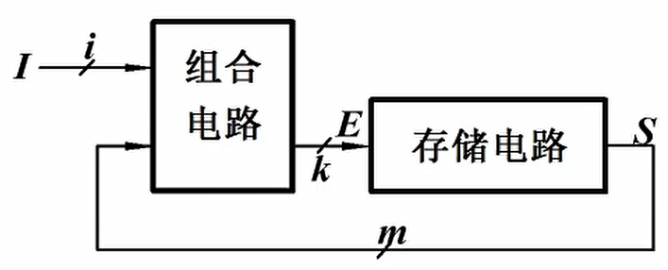

时序电路的一般化模型

时序电路由组合电路、存储电路组成,且电路中存在反馈。

组合电路中没有存储电路,也没有反馈,其输出只与输入和逻辑有关。

双稳态存储单元电路——锁存器与触发器

共同点:具有0和1两个稳定状态,状态确定后能自行保持。一个锁存器或触发器能存储一位二进制码

不同点:锁存器是对电平敏感的存储电路;触发器是对脉冲边沿(上升沿或下降沿)敏感的存储电路。

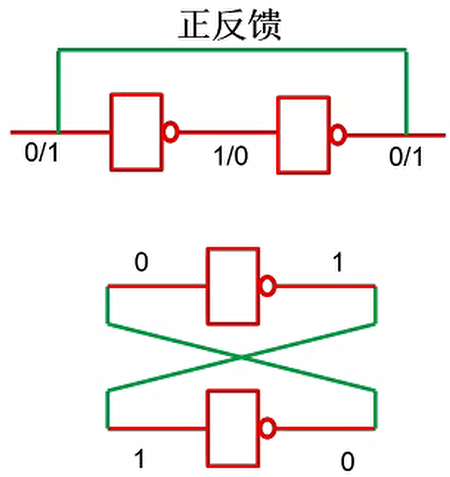

两个反馈

时序电路中存在反馈: \( S^{n+1}=f(I,组合电路,S^n) \) (下章) ;

记忆单元中存在反馈,即锁存器或触发器,在其内部存在反馈

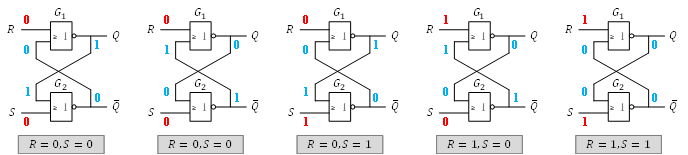

初态: R、S信号作用前Q端的状态,初态用 \(Q^n\) 表示;

次态: R、S信号作用后Q端的状态,次态用 \( Q^{n+1} \)表示;

锁存器

SR锁存器(使用或非门):R为“置0”位,S为“置1”位

\( R=0 \)

\( R=1 \)

\( S=0 \)

\( Q^{n+1}=Q^n \)

\( Q^{n+1}=0 \)

\( S=1 \)

\( Q^{n+1}=1 \)

\( Q^{n+1}=0 \)

触发器的电路结构和工作原理

触发器的逻辑功能